摘要: 設計了以ENC28J60 為核心的以太網接口實現方案, 描述了該系統硬件架構的設計方法。在簡要介紹了以太網控制器ENC28J60 的結構、功能、外圍電路的基礎上, 對ENC28J60 與Atmega16 的SPI 通訊進行了闡述。此方案不僅成本低, 而且可以實現500Kbps 以上的傳輸速率, 滿足了嵌入式系統的Internet 控制要求。

1 引言

隨著Internet 的出現和以太網的迅速發展, 基于以太網的設備控制越來越多。目前市場上大部分以太網控制器采用的封裝均超過80 引腳, 如RTL8019AS、DM9008、CS8900A 等。這些器件不僅結構復雜, 面積龐大, 且系統開銷較大。近來, Microchip推出全球首枚28 引腳獨立以太網控制器ENC28J60, 可為嵌入式系統提供低引腳數、低成本、精簡的遠程通訊解決方案。

2 ENC28J60 網絡接口體系結構

ENC28J60 是帶有行業標準串行外設接口(Serial PeripheralInterface, SPI)的獨立以太網控制器。它符合IEEE 802.3 的全部規范, 采用了一系列包過濾機制以對傳入數據包進行限制。它還提供了一個內部DMA 模塊, 以實現快速數據吞吐和硬件支持的IP 校驗和計算。與主控制器的通信通過兩個中斷引腳(INT和WOL)和SPI 腳(SO、SI、SCK、CS)實現, 數據傳輸速率高達10Mb/s.兩個專用的引腳(LEDA、LEDB)用于連接LED, 進行網絡活動狀態指示。圖1 所示為ENC28J60 的典型應用電路。

ENC28J60 由7 個主要功能模塊組成:SPI 接口, 充當主控制器和ENC28J60 之間通信通道; 控制寄存器, 用于控制和監視ENC28J60; 雙端口RAM緩沖器, 用于接收和發送數據包; 判優器, 當DMA、發送和接收模塊發出請求時對RAM緩沖器的訪問進行控制; 總線接口, 對通過SPI 接收的數據和命令進行解析;MAC 模塊:實現符合IEEE 802.3 標準的MAC 邏輯; PHY 模塊, 對雙絞線上的模擬數據進行編碼和譯碼。ENC28J60 還包括其他支持模塊, 諸如振蕩器、片內穩壓器、電平變換器(提供可以接受5V 電壓的I/O 引腳)和系統控制邏輯。

根據以上說明, ENC28J60 應用于嵌入式網絡接口是非常合適的, 有廣闊的應用發展前景。

3 ENC28J60 在嵌入式網絡接口的應用

3.1 硬件電路設計

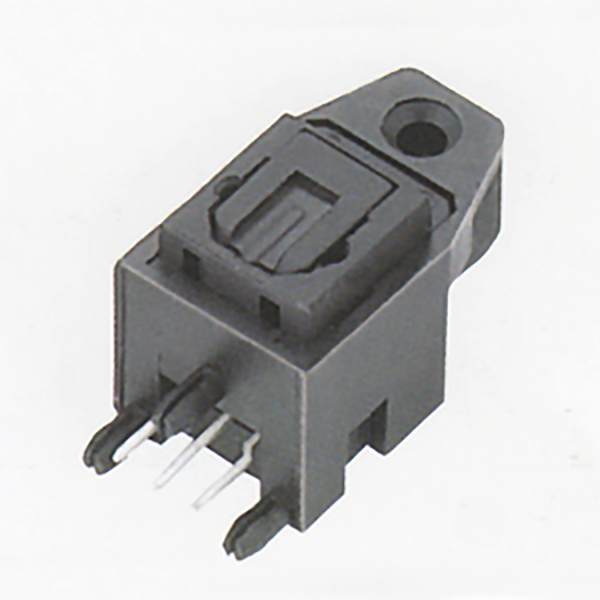

利用ENC28J60 可以構成不同功能的網絡終端節點, 如網絡服務器、帶Internet 功能的設備、遠程監控(數據采集, 診斷)設備等。圖2 所示為基于ENC28J60 的嵌入式網絡接口的硬件電路原理圖。電路中有:2 個LED 狀態指示燈主要用來顯示網絡連接狀態, 包括PHY 是否沖突、連接是否建立、是否接收數據、連接速度、雙工模式等; 必需的偏置電阻R3(2kΩ, 精度為1%);高速局域網電磁隔離模塊(即RJ45 以太網接口), 應用中,ENC28J60 的物理端口與隔離變壓器HR901170A 連接時必須符合IEEE802.3 對物理層規范的要求, 如RJ45 的插孔與隔離變壓器的間隔應盡量小, 輸出和輸入差分信號對的走線要有很好的隔離。

電路中的主控制器采用Atmel 公司的ATmega16 單片機,它具有先進的RISC(精簡指令集計算機)結構、16 kB 可編程Flash 存儲器、512 B 的EEPROM和1 kB 片內SRAM, 具有豐富的外設接口, 其SPI 接口允許ATmega16 與外設進行高速的同步數據傳輸。本設計中ATmega16 SPI 配置為主機模式,ENC28J60 為從設備。ATmega16 的SPI 工作模式由CPOL、CPHA 設置, 根據ENC28J60 的SPI 讀寫時序, ATmega16 的SPI工作模式應設置為模式0.ATmega16 通過將ENC28J60 的CS引腳置低實現與其的同步。SPI 時鐘由寫入到SPI 發送緩沖寄存器的數據啟動, SPI MOSI(PB5)引腳上的數據發送秩序由寄存器SPCR 的DORD 位控制, 置位時數據的LSB(最低位)首先發送, 否則數據的MSB(最高位)首先發送。我們選擇先發送MSB,同時接收到的數據傳送到接收緩沖寄存器, CPU 進行右對齊從接收緩沖器中讀取接收到的數據。應該注意, 當需要從ENC28J60 中讀取多個數據時, 即使ENC28J60 并不需要ATmega16 串行輸出的數據, 每讀取一個數據前都要向SPI 發送緩沖器寫一個數據以啟動SPI 接口時鐘。由于SPI 系統的發送方向只有1 個緩沖器, 而在接收方向有2 個緩沖器, 所以在發送時一定要等到移位過程全部結束后, 才能對SPI 數據寄存器執行寫操作; 而在接收數據時, 需要在下一個字節移位過程結束之前通過訪問SPI 數據寄存器讀取當前接收到的數據, 否則第1 個數據丟失。